Paper Accepted at EUSIPCO 2024: Advancing Green AI Research

Proud to announce that our paper, "Towards Green AI: Assessing the Robustness of Conformer and Transformer Models under Compression,&qu...View more

European Night of Research participation - Bordeaux, France

On September 29, 2023, several members of the FVLLMONTI consortium are invited to take part in the European Researchers' Night event at ...View more

15th Workshop on Parrallel Programming and Run-time Man...

From EPFL, our colleague Amirshahi Alireza participated on the 15th Workshop on Parallel Programming and Run-Time Management Tech...View more

Plenary progress meeting - A collaborative milestones i...

From June 3rd to 5th, we gathered in Toulouse for a series of productive meetings. This event was an excellent opportunity to assess our pro...View more

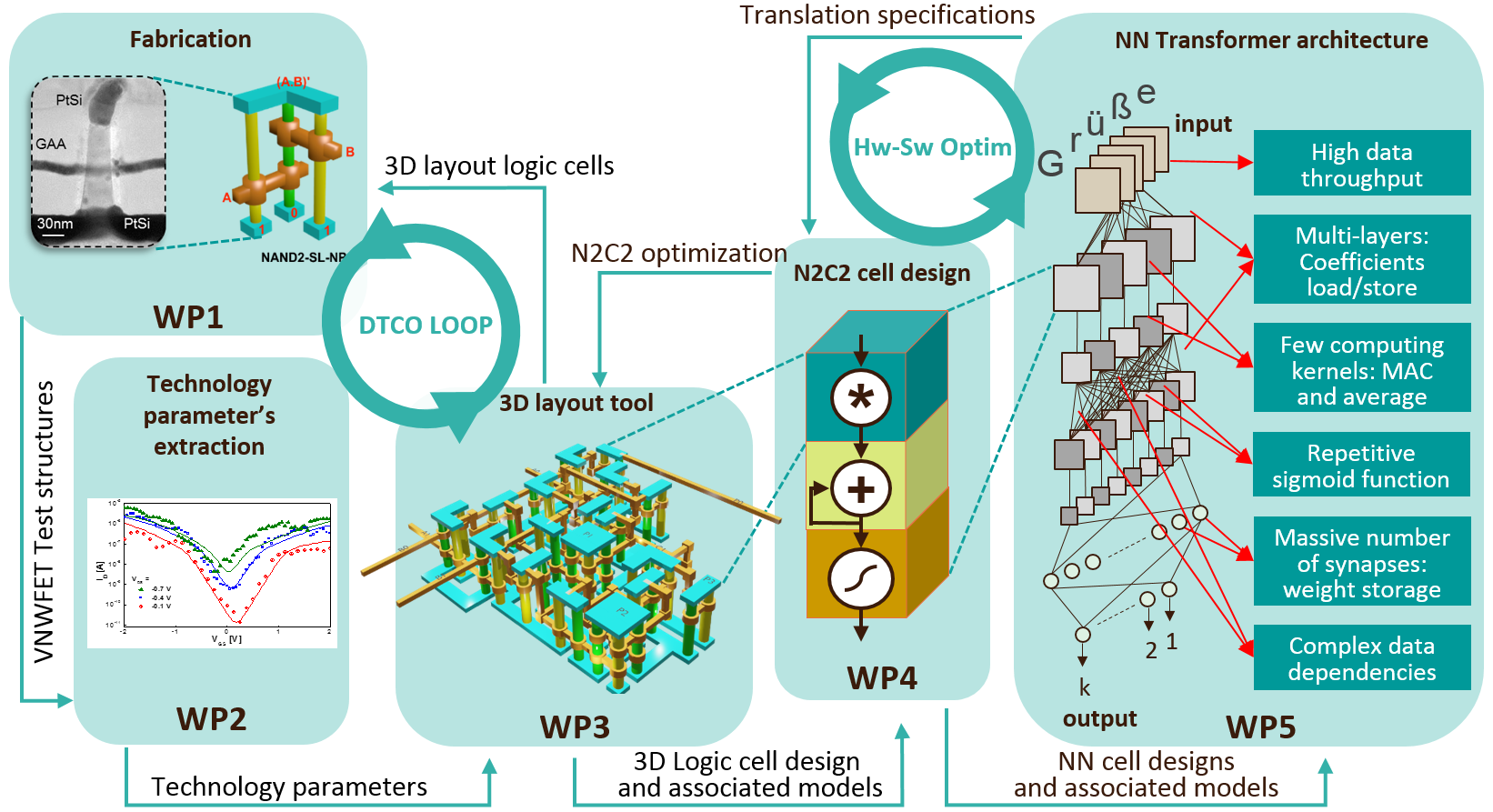

Abstract

In the context of the fourth industrial revolution along with unprecedented growing global interdependencies, an innovative, inclusive and sustainable society is a sound European priority. For many people, the way towards inclusive and sustainable daily life goes through a lightweight in-ear device allowing speech-to-speech translation. Today, such IoT devices require internet connectivity which is proven to be energy inefficient.

While machine translation has greatly improved, an embedded lightweight energy-efficient hardware remains elusive because existing solutions based on artificial neural networks (NNs) are computation-intensive and energy-hungry requiring server-based implementations, which also raises data protection and privacy concerns.

Today, 2D electronic architectures suffer from "unscalable" interconnects, making it difficult for them to compete with biological neural systems in terms of real-time information-processing capabilities with comparable energy consumption. Recent advances in materials science, device technology and synaptic architectures have the potential to fill this gap with novel disruptive technologies that go beyond conventional CMOS technology.

A promising solution comes from vertical nanowire field-effect transistors (VNWFETs) to unlock the full potential of truly 3D neuromorphic computing performance and density.

Through actual VNWFETs fabrication setting up a design-technology co-optimization approach, the FVLLMONTI vision is to develop regular 3D stacked hardware layers of NNs empowering the most efficient machine translation thanks to a fine-grain hardware / software co-optimisation. FVLLMONTI consortium is a strong partnership with complementary expertise and extensive track-records in the fields of nanoelectronics, unconventional logic design, reliability, system‐level design, machine translation, cognition sciences. The consortium is composed of 50% of junior researchers and 90% of first-time participants to FETPROACT.

Objectives

Global objective: Through actual VNWFET fabrication setting up a design-technology co-optimization (DTCO) approach, the FVLLMONTI vision is to develop regular 3D stacked hardware layers of NNs empowering the most efficient machine translation thanks to fine-grain hardware / software co-optimisation.

FVLLMONTI is organized around 4 specific objectives (OBJ) targeting 12 Key Performance Indicators (KPI) mastered through 16 Milestones (MS):

Objective 1: Compactness: From fabricated low-complexity hardware to minimal neural network compute cube (N2C2)

Specific objective 1 (OBJ1) concentrates on the compactness of the elements in the FVLLMONTI value chain from low-level logic blocks up to a critical compute function in N2C2 to ensure the computation resource footprint.

Objective 2: Performance: Energy-delay-product assessment of the computational layer, the embedded Non-Volatile Memory (e-NVM) and interconnects

Specific Objective 2 (OBJ2) is designed to quantify the conventional figure-of-merit energy-delay-product (EDP) towards fast and ultra-low-power data transfer between the e-NVM using ferroelectric-gated VNWFET and the computing layer, thereby addressing the whole FVLLMONTI value chain from low-level logic blocks up to a critical compute function in N2C2.

Objective 3: Validation of the VNWFET technology for live English-French streaming speech recognition to text

Specific Objective 3 (OBJ3) focuses on exploring the use of VNWFET-based 3D logic cells and e-NVM blocks in multiple layers of NNs enabling ultra-compact and energy-efficient Transformers NNs for Automatic Speech Recognition (ASR) and Machine translation (MT). Their compactness and EDP will be compared with general-purpose architectures with CNN accelerators. To validate the approach, the target application is live English-French streaming speech recognition to text.

Objective 4: 3D NN architecture robustness

Specific Objective 4 (OBJ4) assesses the reliability of VNWFET devices at the early step of their development. The impact of the identified wear out failure mechanisms will be appraised on the whole FVLLMONTI value chain: N2C2, 3D NN architecture and up to the ASR and MT application. Beyond the specific translation application, the final intent is to demonstrate the intrinsic 3D NN architecture robustness.

WPs

Work Packages (WPs)

WP1 Fabrication - lead by Guilhem Larrieu (CNRS-LAAS)

WP2Technology parameter's extraction - lead by Chhandak Mukerjee (UBx)

WP3 3D layout tool - lead by Oskar Baumgartner (GTS)

WP4 N2C2 cell design - lead by Ian O'Connor (ECL-INL)

WP5 NN Transformer architecture - lead by Giovanni Ansaloni (EPFL)

KPIs

Key performance indicators (KPIs)

KPI1: Functional logic blocks (LB) using junctionless (JL) VNWFET with two stacked-gate layers and polarity-controllable (PC) VNWFETs with one stacked-gate layer

KPI2: Functional e-NVM cell using hafnium oxide ferroelectric-gated VNWFET. Data retention and endurance suitable for Logic-In-Memory (LiM) Applications

KPI3: Area assessment for 1-bit full adder designs featuring reconfigurable and/or non-volatile functionality

KPI4: EDP assessment for JL VNWFETs, ION of at least 300 µA/µm at a supply voltage below 0.9V with scaled gate length

KPI5: EDP assessment for PC VNWFETs, ION of at least 10 µA/µm at a supply voltage below 2 V

KPI6: EDP assessment for read and write operation of a single transistor ferroelectric VNWFET cell with 3 V write voltage and 2 V operation voltage or below

KPI7: EDP assessment of 1-bit FA designs exploiting reconfigurability and/or e-NVM function

KPI8: NN compression size

KPI9: For ASR and MT

KPI10: Word Error Rate (WER) on read English and French

KPI11: Bi-Lingual Evaluation Understudy (BLEU) score

KPI12: Intrinsic 3D NN architecture robustness, irrespective of the application: Architectural Vulnerability Factor (AVF)

This project has received funding from the European Union’s Horizon 2020 research and innovation programme under grant agreement No 101016776.

Check our results on the CORDIS plateform: https://cordis.europa.eu/project/id/101016776/fr

This publication reflects the views only of the author, and the Commission cannot be held responsible for any use which may be made of the information contained therein.

graph - chart

news

Poster presentation Announcement: Usefulness of Emotional Prosody in Neural Machine Translation

2024-06-05

.jpg)

Invited paper at IEDM 2021, the 67th Annual International Electron Devices Meeting

2021-06-14

events

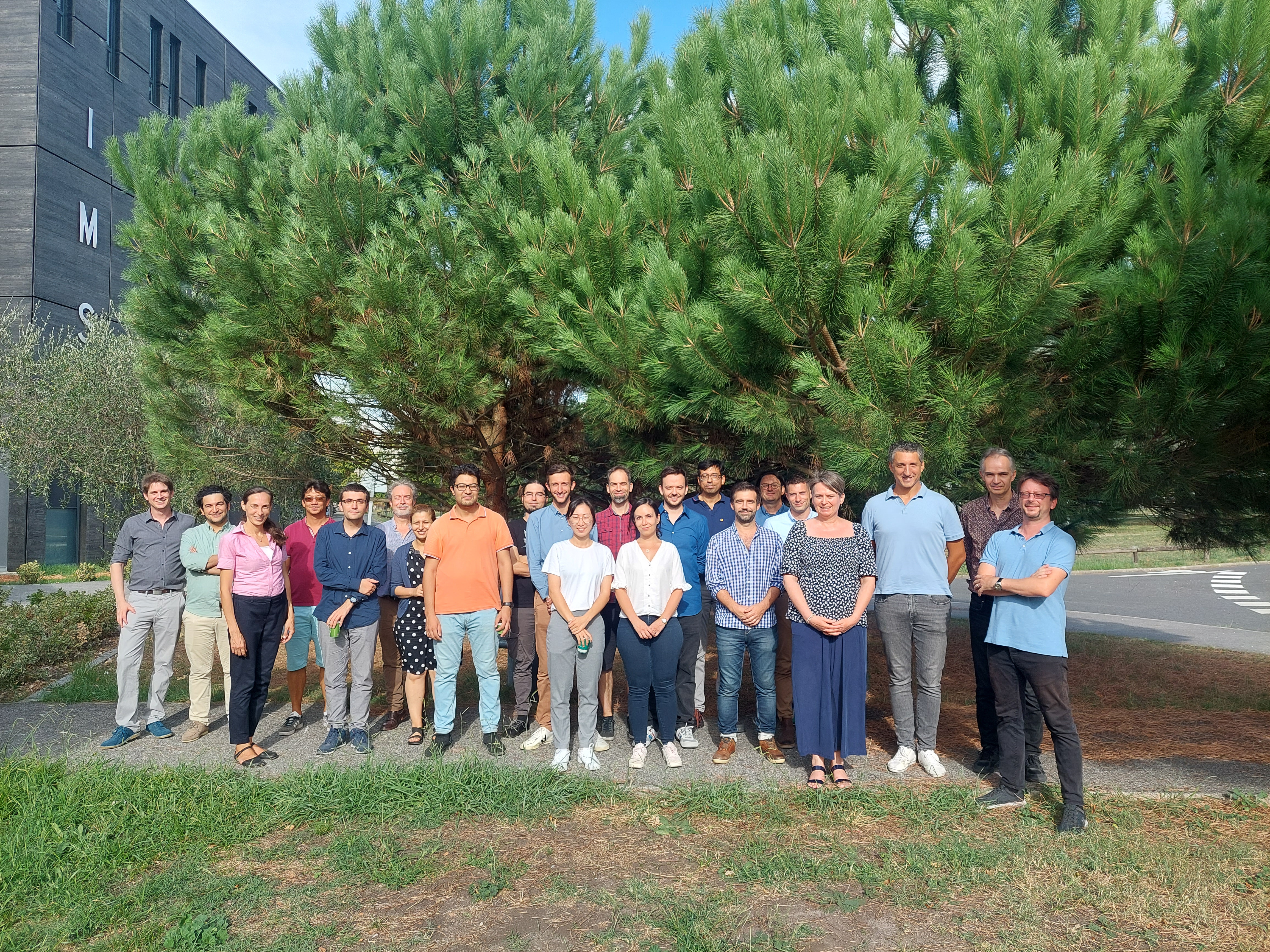

Plenary Session in Toulouse: - How we chose to go towards the project end

From June 3 to 5, the FVLLMONTI project consortium gathered in Toulouse for a pivotal plenary session. The event brought together 18 participants to review and discuss the project's advancements and outline the strategic direction for its remaining duration.

During the meeting, we delved into the progress made, focusing on research data management and the results produced so far. We also addressed the practical implementation of the Data Management Plan (DMP), ensuring alignment with our project's objectives.

Participants were treated to a comprehensive tour and presentation of the LAAS CNRS laboratory, offering insights into its cutting-edge facilities and ongoing research. Additionally, a dedicated session facilitated targeted technical exchanges, tailored to the specific preferences and requests of each partner.

The plenary session concluded with discussions on the project's final phase, including its closure and the planning of a follow-up project. This event was instrumental in ensuring a cohesive and strategic approach as we advance towards the successful completion of the FVLLMONTI project.

RP2 EU Review Meeting: A Decisive Checkpoint

The EU review meeting, set for May 17th on Zoom, is a vital assessment to evaluate our project's progress against its work plan and objectives. It's not just a routine check but a significant determinant for future funding.

This session aims to scrutinize the alignment of our efforts with the outlined milestones and deliverables. Its outcome influences continued financial support, making it crucial for our project's lifecycle. We'll present our achievements and address any variances from our initial plans, showcasing our adherence to goals and efficient fund use.

The meeting facilitates a critical dialogue between project members and EU reviewers, focusing on technical, financial, and impact evaluations. It's an opportunity to reaffirm our commitment and discuss improvements.

Details and the agenda will be shared with participants to ensure a streamlined and productive review. This meeting is fundamental, reflecting our dedication to project success and accountability.

EU Review experts retained:

TECHNICAL MONITORS

- Dimitris tsoukalas NTUA Grece

- Marian Verhelst KU Leuven

- Manil Dev Gomony, Assistant Professor - Eindhoven University of Technology - Researcher at Nokia Bells Labs

IR EXPERT:

- ZAMBRANO Raffaele STMicroelectronics

Review meeting Rehearsal - Science is never tired to be professionnal

On May 13, 2024, we held a crucial preparation meeting in anticipation of our upcoming Review Meeting with the European Commission. This session allowed our consortium members to practice delivering oral presentations on the current progress of our project.

The presentations were subject to constructive feedback and pertinent critiques, ensuring that each contribution aligns with the meeting's objectives and framework. We paid close attention to adhering to the agenda, particularly regarding the time allocated for each presentation, to ensure a smooth and efficient flow during the official meeting with the Commission.

Plenary Progress Meeting n°5

From the 15/11/2023 to the 16/11/2023, at Vienna, Austria.

The purpose of this meeting is to review the progress of our ongoing FVLLMONTI project, and to ensure that we remain on track towards our shared goals.

Over the course of this meeting, we discussed the issues that our WPL have faced since march 2023, the implemented solutions to solve them, and the ideas or concrete steps that we need to implement, in order to continue moving forward.

AGENDA:

Day 1

- WP7 Progresses: Meeting objectives and future actions (Cristell MANEUX, Axel POMEPUI-GUIHARD)

- WP5 Progresses: CNN Architecture for talk (Giovanni ANSALONI)

- WP4 Progresses: VNWFET based 3D NN compute cube design (N²C²) (Ian O'CONNOR)

- WP3 Progresses: TCAD And compact modeling (Oskar BAUMGARTNER)

Day 2

- WP2 Progresses: Parameter extraction ( Chandak MUKHERJEE)

- WP1 Progresses: Fabrication of VNW techonologies from devices to logic blocks ( Guilhem LARRIEU)

- WP6 Progresses: Dissemination & Exploitation activities ( Jens TROMMER, Axel POMEPUI GUIHARD)

- Outlook and plans for next steps

It is also an opportunity to share knowledge and expertise too, with view to prepare the second EU review, incoming in february 2024; and ensure that we are all working together effectively to produce innovative, quality, scientific research; respecting our legal and financial obligations towards the European commission.

European Night of research participation

On September 29, 2023, several members of the FVLLMONTI consortium are invited to take part in the European Researchers' Night event at Cap Sciences in Bordeaux.

Our involved searchers and members are the following ones:

- Chhandak MUKHERJEE, WP2L as an invited searcher on individual and dedicated activities: speed searching, future and science discussion with publics.

- Marina DENG, WP2M, as an invited searcher on individual activities: speed searching, future and science discussion with publics.

- Cristell MANEUX, WP7L as an invited searcher on grouped activities: short conference with cultural intermediary.

- Yifan WANG, WP2D, as an invited PhD student, on individual and grouped activities: short conference with cultural intermediary; meet in the dark and discussion with publics.

- GUIHARD Axel, WP7M, as EU project manager, event organizator and coordonator.

This event, led by the University of Burgundy for the French part of this European event, is an important part of our dissemination activities to the general public. All ages and people are met during this night.

On the program: workshops and demonstrations, participation in conferences aimed at popularizing our on-site activities, prospecting and presentation of European projects through permanent representation at the event.

LINKS:

To get more informations about the event: https://www.cap-sciences.net/au-programme/evenement/grand-public/nuit-europeenne-des-chercheur-euses-2023/

Our apparition on CNRS revues: https://www.aquitaine.cnrs.fr/fr/cnrsinfo/retour-sur-la-nuit-europeenne-des-chercheures-2023

2nd Advisory Board Meeting

The secondAdvisory Board meeting of the FVLLMONTI project took place on 4 of July 2023. It has been tenued during a Zoom remote session.

We've got the pleasure to welcome our new AB Member for the first time: Gérard CHOLLET.

AB Members representing:

- CEA-Leti: Thomas Ernst

- TSMC: Katherine Chiang

- Thales avionics: Sylvain Hourlier

- NUI Galwa Data Science Institute: John McCrae

- Nanyang Technology University: Mohamed Sabry Aly

- CNRS, Emeritus Dir: Gérard Chollet

Energy Efficient Embedded AI - Bordeaux Summer School

Bordeaux Summer School

19/06/2023-23/06/2023

The E3AI summer school is open to second year Master students, doctoral students, post-doctoral fellows, researchers and professionals with an interest in embedded artificial intelligence, deep learning, neuromorphic computing, natural language processing, spintronics and 6G communications.

Course content will address the consequent skill gap between embedded technology and deep learning applications, and will equip participants with the interdisciplinary knowledge and skills needed to develop innovative circuit architectures and execute data intensive applications on resource-constrained devices.

This summer school is supported by FVLLMONTI, Hermes and RadioSpin, three H2020 European projects, and is co-organised with the Green AI (GrAI) chair in artificial intelligence and the IEEE Circuits and Systems Society. The event is the first in a series of similar bi-annual events organised by and for the Embedded Artificial Intelligence (EAI) transdisciplinary community.

Plenary Progress Meeting n°4

From the 22/03/2023 to the 23/03/2023, at the EPFL in Lausanne, Switerzland.

The purpose of this meeting is to review the progress of our ongoing FVLLMONTI project, and to ensure that we remain on track towards our shared goals.

Day 1

- WP7 Progresses: Meeting objectives and future actions (Cristell MANEUX, Axel POMEPUI-GUIHARD)

- WP5 Progresses: CNN Architecture for talk (Giovanni ANSALONI)

- WP4 Progresses: VNWFET based 3D NN compute cube design (N²C²) (Ian O'CONNOR)

- WP3 Progresses: TCAD And compact modeling (Oskar BAUMGARTNER)

Day 2

- WP2 Progresses: Parameter extraction ( Chandak MUKHERJEE)

- WP1 Progresses: Fabrication of VNW techonologies from devices to logic blocks ( Guilhem LARRIEU)

- WP6 Progresses: Dissemination & Exploitation activities ( Jens TROMMER, Axel POMEPUI GUIHARD)

- Outlook and plans for next steps

Over the course of this meeting, we discussed the issues that our WPL have faced since months ago, the implemented solutions to solve them, and the ideas or concrete steps that we need to implement, in order to continue moving forward. It was for us an opportunity to share knowledge and expertise too; and ensure that we are all working together effectively to produce innovative, quality, scientific research.

EU Review Meeting-Reporting Period 1

Holding our first review meeting with renowned European experts for our project, funded by the European Commission. Stay informed as we share updates and insights from this collaboration, shaping the future of groundbreaking solutions.

The purpose and role of EU experts in a review meeting for an EU funded project are to assess the project's progress, achievements, and compliance with the set objectives and guidelines, providing valuable feedback and recommendations to ensure its successful implementation and alignment with EU's objectives

You can have access to the project related EU data. We invite you to take information of all our activities and general frame of our activities on:

https://cordis.europa.eu/project/id/101016776/fr

Plenary Progress Meeting n°3

In the general project lifecycle progresses, at M12, the purpose of this meeting is to review the progress of our ongoing FVLLMONTI project, one year after its kick-off, and to ensure that we remain on track towards our shared goals.

Over the course of this meeting, we discussed the issues that our WPL faced since the last PPM, the implemented actions done until the meeting.It was for us an opportunity to ensure that we are all working together effectively to produce innovative, quality, scientific research.

Plenary Progress Meeting n°2

A one day progress meeting, tenued at the University of Bordeaux, France

The purpose of this meeting is to review the progress of our ongoing FVLLMONTI project, and to ensure that we remain on track towards our shared goals.

Over the course of this meeting, we discussed the issues that our WPL faced since the begining of the project, the implemented actions done until the meeting, and the ideas or concrete steps that we need to implement, in order to continue moving forward. It was for us an opportunity to ensure that we are all working together effectively to produce innovative, quality, scientific research.

1st Advisory Board Meeting

The first Advisory Board meeting of the FVLLMONTI project took place on 21 of June 2021 at the Laboratoire de l'Intégration du Matériau au Système (IMS) in Bordeaux (France). Also, a remote session was available.

AB Members representing:

- CEA-Leti: Thomas Ernst

- TSMC: Katherine Chiang

- Thales avionics: Sylvain Hourlier

- NUI Galwa Data Science Institute: John McCrae

- Nanyang Technology University: Mohamed Sabry Aly

Plenary Progress meeting n°1

With view to frame the general habits, ways of working and practices which permit a well follow-up and management of our project lifecycle: a general meeting has been tenued, to inform all our partners about the decided process to follow in question.

Project management centred meeting axis.

Georgetta BORDEA is in charge of the project management. Working with Cristell Maneux as WP7 Leaders, both of them created the FVLLMONTI way of doing.

- Performance & Excellence

- Communication

- Trust & Resilience

- Respect for everyone's time

- Professionnalism & Habits

FVLLMONTI project Kick-off Meeting

The mission and objective of this meeting is to take advantage of, lay the foundations for, and take up the challenges that the consortium may face in the various sectors of activity targeted by its intervention and research, for the project but above all in the projections for the future of which it is the subject.

We're a diverse, skilled consortium, ready to drive innovation and foster collaboration.

Meeting discussion points expectations:

Project Overview: Goals and scope framing.

Work Packages: Divide tasks and set a common timeline.

Resource Allocation: Fix the allocate funds and personnel concerns.

Ethical Considerations: AI related concerns and developpement framing.

Risk Management: Mitigate potential setbacks and fix risks.

Communication: Foster open collaboration within and outside the consortium.

Data Management: Secure and comply with GDPR.

Dissemination: Share findings and maximize impact.

publications

Towards Green AI : Assessing the Robustness o...

2024-08-26

EUSIPCO is the premier European conference on signal processing. The 32nd edition will be held in Lyon, at the Lyon Convention Center, locat...

View moreUsefulness of Emotional Prosody in Neural Ma...

2024-06-05

Usefulness of Emotional Prosody in Neural Machine Translation

View moreUnderstanding the substrate effect on de-embe...

2024-04-18

In this paper, we present the fabrication, characterization, and electromagnetic simulation of open pad test structures on silicon-on-insula...

View moreThe 3D Neural Network Compute Cube (N2C2) Con...

2024-03-28

This multi-partner-project contribution introduces the midway results of the Horizon 2020 FVLLMONTI project. In this project we develop a ne...

View moreStrategies for Characterization and Parameter...

2023-11-10

In the era of emerging computing paradigms and artificial neural networks, hardware and functionality requirements are in the surge. In orde...

View moreAdvancements in HZO Layer Engineering for Ult...

2023-10-23

The Von Neumann architecture has been the dominant philosophy behind every computing system over the past decades, consisting of a computing...

View moreREMOTE: Re-thinking Task Mapping on Wireless ...

2023-10-16

2.5D Systems-on-Package (SoPs) are composed by several chiplets placed on an interposer. They are becoming increasingly popular as they enab...

View moreA 16-bit floating-point near-sram architectur...

2023-10-16

State-of-the-art Artificial Intelligence (AI) algorithms, such as graph neural networks and recommendation systems, require floating-point c...

View moreNanoscale Thermal Transport in Vertical Gate-...

2023-10-11

Today, extensive research has focused on heat propagation in emerging nanoelectronic devices. With advances in the fabrication of nanowire (...

View moreLayer-Wise Learning Framework for Efficient D...

2023-10-11

The development of low-power wearable systems requires specialized techniques to accommodate their unique requirements and constraints. Whil...

View moreNanoscale Thermal Transport in Vertical Gate-...

2023-10-10

In this article, we present the first detailed experimental study of electrothermal effects in 3-D vertical gate-all-around (GAA) junctionle...

View moreA Study of the Variability and Design Conside...

2023-10-02

In this work a TCAD model of a ferroelectric VNAND device is developed and validated against experimental data. After its accuracy is demons...

View moreCompact Metal-Ferroelectric-Insulator-Semicon...

2023-09-27

Ferroelectric-based transistors (FeFETs) are an important emerging technology with applications both as conventional memories and in emergin...

View moreCompact Metal-Ferroelectric-Insulator-Semicon...

2023-09-27

Ferroelectric-based transistors (FeFETs) are an important emerging technology with applications both as conventional memories and in emergin...

View moreCompact Metal-Ferroelectric-Insulator-Semicon...

2023-09-27

Ferroelectric-based transistors (FeFETs) are an important emerging technology with applications both as conventional memories and in emergin...

View moreElectrothermal modeling of junctionless verti...

2023-09-14

This work presents a comprehensive analysis of electrothermal effects in emerging 3D vertical junctionless nanowire transistors (VNWFETs) us...

View moreA Study of the Variability and Design Conside...

2023-09-11

In this work a TCAD model of a ferroelectric VNAND device is developed and validated against experimental data. After its accuracy is demons...

View moreA Study of the Variability and Design Conside...

2023-09-11

In this work a TCAD model of a ferroelectric VNAND device is developed and validated against experimental data. After its accuracy is demons...

View moreOverflow-free compute memories for edge AI ac...

2023-09-09

Compute memories are memory arrays augmented with dedicated logic to support arithmetic. They support the efficient execution of data-centri...

View moreDemonstration of a p-type Junctionless Silico...

2023-09-04

Author:T. Mauersberger, J. Trommer, G. Galderisi, M. Knaut, D. Pohl, A. Tahn, B.

View more3D Logic circuit design oriented electrotherm...

2023-08-28

This work presents new insights into 3-D logic circuit design with vertical junctionless nanowire FETs (VNWFET) accounting for underlying el...

View more3D Logic circuit design oriented electrotherm...

2023-08-28

Authors: Sara MANNAA; Arnaud POITEVIN; Cedric MARCHAND; Damien DELERUYELLE;Bastien DEVEAUTOUR; Alberto BOSIO; Ian O'CONNOR; C...

View moreVariable Scale Pruning for Transformer Model ...

2023-08-23

Transformer models are being increasingly used in end-to-end speech recognition systems for their performance. However, their substantial si...

View moreVNWFET-Based Technology: From Device Modellin...

2023-07-04

Vertical Nanowire Field Effect Transistors (VN-WFETs) are an emerging technology with significant potential to reduce footprint and conseque...

View moreThermal consideration in nanoscale gate-all-a...

2023-06-12

Devolvement of high-performance logic application in sub-20 nm technology node has gained significant attention due to their improved electr...

View moreAdvanced contacts on 3D nanostructured channe...

2023-06-09

Gate-all-around (GAA) transistors are anticipated to have a substantial impact in achieving logic scaling in the nanometer technology node r...

View moreEnergy-Efficient Computation-In-Memory Archit...

2023-06-01

Deep Learning (DL) has recently led to remark-able advancements, however, it faces severe computation related challenges. Existing Von-Neuma...

View moreCross-shape reconfigurable field effect trans...

2023-06-01

Cigdem Cakirlar, Maik Simon, Giulio Galderisi, Ian O'Connor, Thomas Mikolajick, Jens Trommer

View moreFine-grained analysis of the transformer mode...

2023-03-23

In automatic speech recognition, deep learning models such as transformers are increasingly used for their high performance. However, they s...

View moreBit-Line Computing for CNN Accelerators Co-De...

2023-01-23

By supporting the access of multiple memory words at the same time, Bit-line Computing (BC) architectures allow the parallel execution of bi...

View moreTiC-SAT: Tightly-coupled Systolic Accelerator...

2023-01-16

Transformer models have achieved impressive results in various AI scenarios, ranging from vision to natural language processing. However, th...

View moreSystem-Level Exploration of In-Package Wirele...

2023-01-16

Multi-Chiplet architectures are being increasingly adopted to support the design of very large systems in a single package, facilitating the...

View moreChallenges in Electron Beam Lithography of Si...

2022-11-08

The fabrication of semiconductor nano-structures is one of the most important tools for microelectronic research. Due to the high gate coupl...

View moreAnalysis of an Inverter Logic Cell based on 3...

2022-10-03

Vertical Nanowire Junction-less Transistors (VN-WFET) are a promising technology for designing energy-efficient neural networks. This work p...

View moreFull System Exploration of On-Chip Wireless C...

2022-09-19

In order to develop sustainable and more powerful information technology (IT) infrastructures, the challenges posed by the “memory wal...

View moreTransformer model compression for end-to-end ...

2022-08-29

Authors : Leila Ben Letaifa, Jean-Luc Rouas

View moreReconfigurable field effect transistors: A te...

2022-08-10

With classical scaling of CMOS transistors according to Dennard’s scaling rules running out of steam, new possibilities to increase th...

View moreA Logic Cell Design and routing Methodology S...

2022-08-05

New emerging Vertical NanoWire Field-Effect Transistors (VNWFET) appear promising for compact energy effcient computing architectures, still...

View moreReconfigurable field effect transistors: A te...

2022-08-01

With classical scaling of CMOS transistors according to Dennard’s scaling rules running out of steam, new possibilities to increase th...

View moreExtraction of small-signal equivalent circuit...

2022-08-01

Bruno Neckel Wesling, Marina Deng, Chhandak Mukherjee, Magali de Matos, Abhishek Kumar, Guilhem Larrieu, Jens Trommer, Thomas Mikolajick, Cr...

View moreHardware/software co-design vision for deep l...

2022-08-01

The growing popularity of edgeAI requires novel solutions to support the deployment of compute-intense algorithms in embedded devices. In th...

View moreChallenges in Electron Beam Lithography of Si...

2022-07-04

Cigdem Cakirlar, Giulio Galderisi, Christoph Beyer, Maik Simon, Thomas Mikolajick, Jens Trommer

View moreError Resilient In-Memory Computing Architect...

2022-06-06

The growing popularity of edge computing has fostered the development of diverse solutions to support Artificial Intelligence (AI) in energy...

View moreReconfigurable Field Effect Transistors: A Te...

2022-05-11

T Mikolajick, G Galderisi, S Rai, M Simon, R Böckle, M Sistani, C Cakirlar, N Bhattacharjee, T Mauersberger, A Heinzig, A Kumar, WM Web...

View moreOn the Modeling of Polycrystalline Ferroelect...

2022-04-29

Authors: Thesberg, Mischa; Alam, Md Nur K.; Truijen, Brecht; Kaczer, B.; Roussel, Philippe. J.; Stanojevic, Zlatan; Baumgartner, Oskar; Scha...

View moreOn the Modeling of Polycrystalline Ferroelect...

2022-04-29

Due to the potential for technological application, there has been an explosion of interest in heavily polycrystalline ferroelectric nanofil...

View moreINCLASS: Incremental Classification Strategy ...

2022-03-14

Wearable Health Companions allow the unobtrusive monitoring of patients affected by chronic conditions. In particular, by acquiring and inte...

View morePatterning and integration issues of doped na...

2021-01-01

Abhishek Kumar, Aurélie Lecestre, Jonas Müller , Guilhem Larrieu

View moreSingle-step reactive ion etching process for ...

2021-01-01

Authors: Tom Mauersberger, Jens Trommer, Saurabh Sharma, Martin Knaut, Darius Pohl, Bernd Rellinghaus, Thomas Mikolajick, André Heinz...

View moreCompact Modeling of 3D Vertical Junctionless ...

2021-01-01

Mukherjee, C., Larrieu, G., Maneux, C. 2020 Joint International EUROSOI Workshop and International Conference on Ultimate Integration o...

View moreModelling of vertical and ferroelectric junct...

2021-01-01

Authors: C. Maneux, C. Mukherjee, M. Deng, M. Dubourg, L. Reveil, G. Bordea, A. Lecestre, G. Larrieu, J. Trommer, E.T. Breyer, S. Slesazeck,...

View more3D Logic Cells Design and Results Based on Ve...

2021-01-01

Poittevin, A., Mukherjee, C., O’Connor, I., Maneux, C., Larrieu, G., Deng, M., Le Beux, S., Marc, F., Lecestre, A., Marchand, C., Kuma...

View moreCompact modeling of 3D vertical junctionless ...

2021-01-01

Mukherjee, C., Poittevin, A., O'Connor, I., Larrieu, G., Maneux, C.Solid-State Electronics, 183, art. no. 108125.

3D Logic Cells Design and Results Based on Ve...

2021-01-01

Mukherjee, C., Deng, M., Marc, F., Maneux, C., Poittevin, A., O'Connor, I., Beux, S.L., Marchand, C., Kumar, A., Lecestre, A., Larrieu,G...

View moredocuments

Article - HiPEAC Conference 2022

FVLLMONTI LEAFLET 2024

Invited Presentation - FETCH Conference 2023 C. Maneux - Invited Presentation at FETCH Summer School 2023. How to reinvent the value chain with emerging technologies and new computing paradigms? Challenges in characterization, modelling and circuit design.

Leaflet Back

Leaflet Front

D.1.1_FVLLMONTI_P2-Larrieu-20220902_Elementary VNWFET devices – JL (PU)

D.1.2 - Fabrication of elementary VNWFET devices (JL and PC) - improved version

D.2.1_Thermal impedance and trap extraction_FVLLMONTI_P1-MUKHERJEE-230531 (PU)

D.2.3_Parasitic Element Extraction_FVLLMONTI_P1‐MUKHERJEE‐230222 (PU)

D.4.1_FVLLMONTI_P3 ECL_Library of optimized VNWFET-based logic cells (PU)

D4.3_Versatile and scalable 3D interconnect framework_FVLLMONTI_P3-ECL-INL-20231031 (PU) - Report on the versatile and scalable 3D architectural interconnect framework

D4.4_Scaled-down N2C2 design_FVLLMONTI_P3-ECL-20231130 (PU) - Report on scaled-down N2C2 design

D.4.5_Virtual scalable N2C 2 design and Pareto-front data_FVLLMONTI_P3-ECL-INL-20210831 (PU) - Virtual scalable N2C2 design and Pareto-front data (initial version) - M6+2 - P3 ECL-INL, P5 EPFL

D.5.1_Pre-trained speech ASR/MT model and use cases - V1_FVLLMONTI_P1-UBX-20210831 V1 - (PU) - This document presents the achievements of the partners participating to WP5 during the first semester of the FVLLMONTI project. In this period, work has focused on developing Automatic Speech Recognition (ASR) and Machine Translation (MT) systems using state-of-the-art methods, including neural network transformer architecture. Such activities are the first step towards the WP objectives, as they establish a baseline toward run-time and energy-wise optimization strategies that will be explored for the remainder of the project duration.

D5.2_Pre-trained speech ASRMT_FVLLMONTI_P1-UBX-20231231 (PU)

D.5.3 Architecture library multi-objective trade-offs and calibrated thermal models V1 (PU) - First version of architecture library, multi-objective trade-offs and calibrated thermal models

D.5.5 Co-optimized hardware-NN architecture for ASR MT V1 (PU) - First report on the co-optimized hardware/NN architecture for ASR/MT

D5.7_FVLLMONTI_P5-EPFL-20231231 (PU)

D.6.1_FVLLMONTI_P6-NLB-20210831 (PU) - Project Website and social network accounts

D.6.2_FVLLMONTI_P1-UBx-220201 (PU) - Plan for dissemination of the results - Y1

D.6.3_FVLLMONTI_P1-UBX_20230228 (PU) - Plans for disseminations of the results Y2

D.6.6_FVLLMONTI_P1-UBX-20210831 (PU) - Data Management Plan

D.6.6_FVLLMONTI_P6 2 -NAMLAB-GGMBH-20210831 (PU) - Generated datasets for the FVLLMOTNI project

D.6.7_FVLLMONTI_P6-NMLB_2023 (PU) - Technology impact and exploitation innovation Y1

D.6.8_FVLLMONTI_P6-NLB-220228 (PU) - Technology impact and exploitation innovation Y2

contact us

Do you want to be part of something innovative? Our project is not just any endeavor, it's an opportunity to make a difference in european science and worldwide one. If you're as excited as we are and have questions, ideas, or simply want to learn more, this is your chance. Reach out to us with a dedicated message, and let's shape the future together !

Email: contact@fvllmonti.eu

LinkedIn: https://www.linkedin.com/in/fvllmonti-project/

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)

.png)